英特尔详解Sapphire Rapids-SP至强CPU的芯片堆栈与互连设计

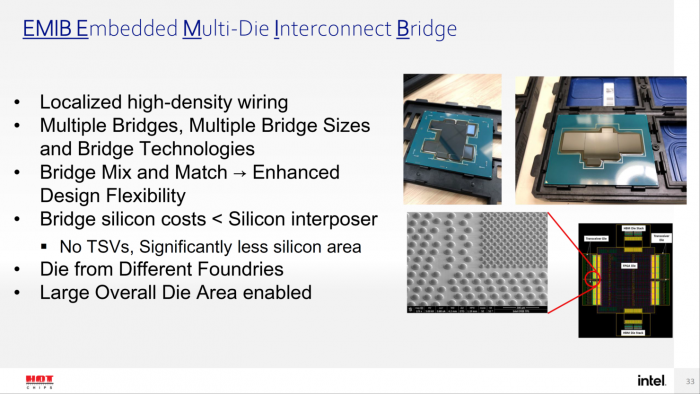

英特尔刚刚披露了与 Sapphire Rapids-SP 至强 CPU 有关的第一条确切消息,即该处理器将通过多芯片设计,以结合主核心芯片 + HBM2E 缓存堆栈。具体说来是,Sapphire Rapids-SP 至强 CPU 将具有 4 个 8-Hi HBM2E 堆栈、14 条 EMIB 互连、且全 XCC 芯片的尺寸约为 400 m㎡ 。

此前,WCCFTech 已经详细介绍过英特尔的 Sapphire Rapids-SP Xeon CPU,但在 HotChip 33 年度会议期间,这家芯片巨头还揭示了更多花絮。

据英特尔所述,Sapphire Rapids-SP 将提供基于两种封装的衍生版本。标准版将采用由四个 XCC 芯片所组成的小芯片设计,尺寸约为 400 m㎡ 。

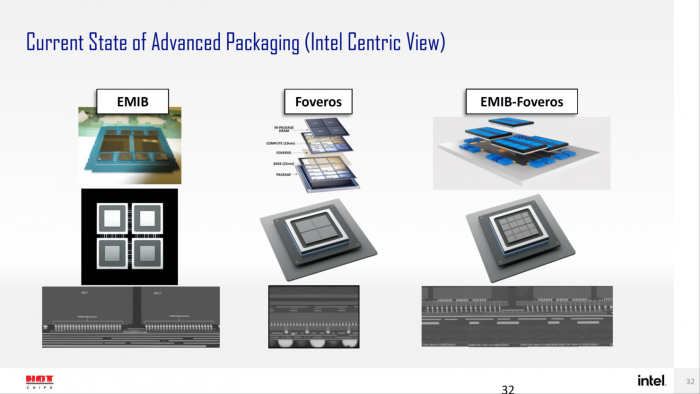

在单个 XCC 之外,顶级 Sapphire Rapids-SP 至强 CPU 还将集成四个芯片,并且会借助 EMIB 互连技术打通彼此 —— EMIB 间距约 55u,核心间距为 100u 。

标准款 Sapphire Rapids-SP 至强芯片具有 10 条 EMIB 互连,完整封装尺寸为 4446 m㎡ 。此外 HBM 衍生版本用到了 14 条 EMIB 互连,以打通内核与 HBM2E 高带宽内存。

四路 HBM2E 内存将采用 8-Hi 堆栈打造,每个堆栈至少拥有 16GB 的 HBM2E 内存,使得 Sapphire Rapids-SP 总计可获得 64GB 内存。

然而 5700 m㎡ 的惊人封装,还是较标准版本大了 28% 左右。即使与近期泄露的 AMD 霄龙 Genoa 相比(12 CCD 封装 / 5428 m㎡),HBM2E 衍生版本的 Sapphire Rapids-SP 还是大了 5%(标准封装小 22%)。

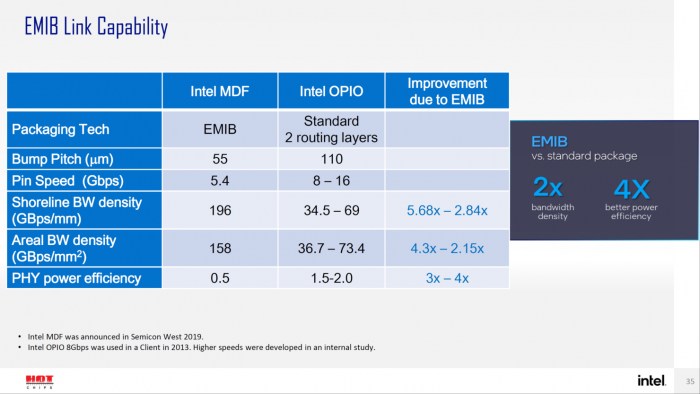

英特尔还表示,与标准封装设计相比,EMIB 互联总线还可提供两倍的带宽密度、以及 4 倍的能效效率改进。

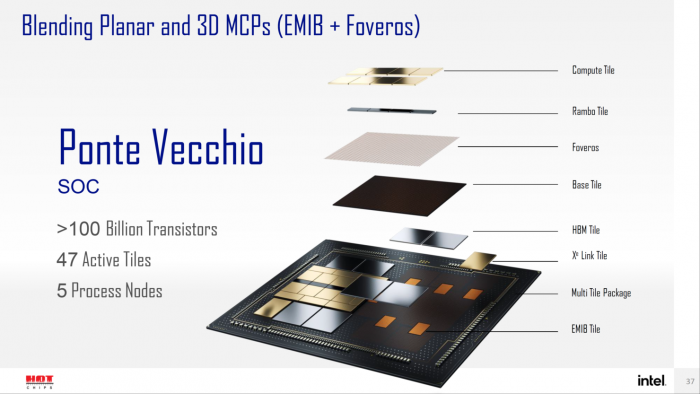

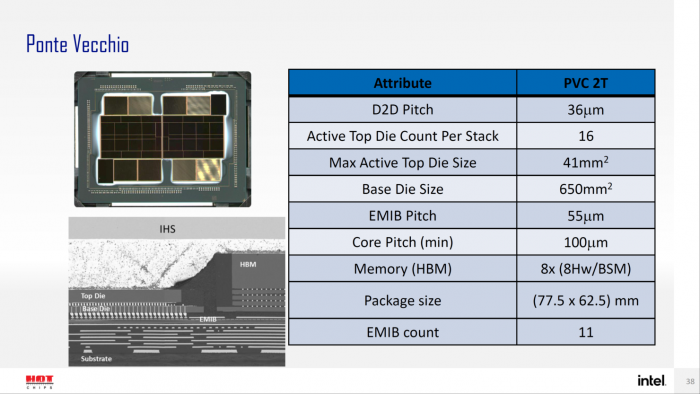

此外,这家芯片巨头详细介绍了其基于 Xe-HPC 架构的 Ponte Vecchio 旗舰 GPU 的封装和芯片尺寸。可知该芯片将由 2 个瓦片组成,且每堆栈有 16 个芯片(41 m㎡)。

每个计算块(Compute Tile)的大小为 650 m㎡,且 Ponte Vecchio GPU 使用了 8 个 HBM 8-Hi 堆栈、并包含总共 11 条 EMIB 互连,整个 Ponte Vecchio 封装的尺寸为 4843.75 m㎡ 。

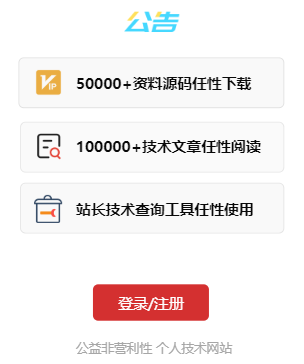

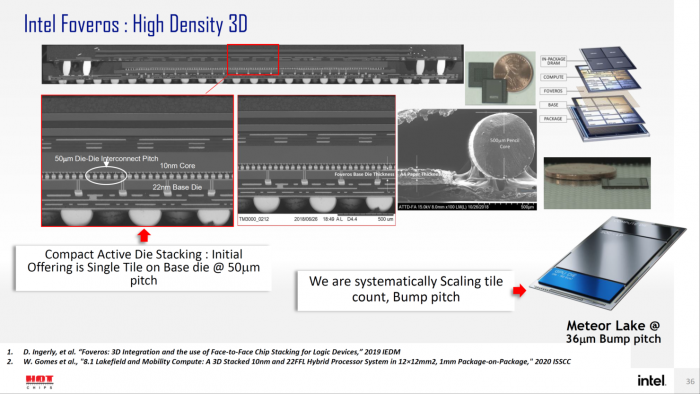

最后是使用高密度 3D Forveros 封装的 Meteor Lake CPU,可知其凸点(Bump Pitch)间距为 36u 。

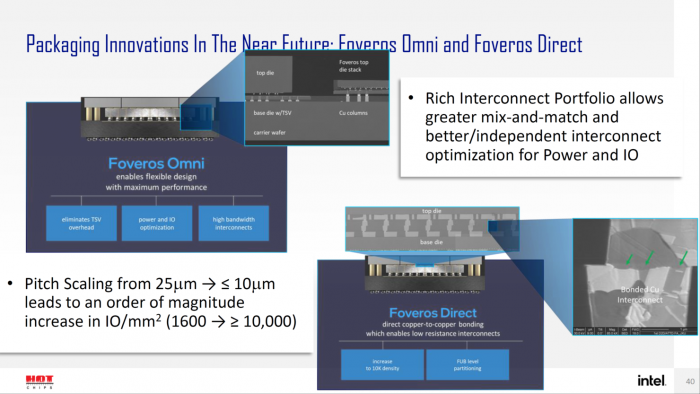

随着 Forveros Omni 和 Forveros Direct 进入晶体管开发的“埃时代”(Angstrom Era),英特尔将拥有诸多面向下一代解决方案的高级封装设计 IP 。

来自: cnBeta